Bright lights, big pity Pg 54

To hack the brain, you need to hack the hardware Pg 9

**Signal Integrity:** Time invariance Pg 18

Design Ideas Pg 43

Expanding patchwork of state e-waste laws Pg 50

6

C

YOU NEED IT

VOICE OF THE ENGINEER

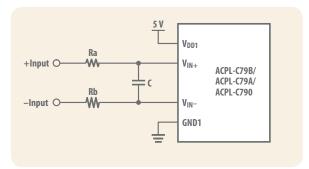

For samples, design kits and whitepapers on these topics, go to: www.avago responsecenter.com/441

### Avago Technologies. 45 Years of Innovation Brings Your Imagination to Life.

Avago Technologies is a leading supplier in III-V compound and silicon semiconductor design and processing.

Avago provides an extensive range of analog, mixed signal and optoelectronics components that are backed by over 5,000 patents and applications to approximately 40,000 end customers.

With a heritage of technical innovation dating back 45 years, over 1,000 talented design and product engineers, strong customer service support, Avago's products serve four diverse end markets: wireless communication, wired infrastructure, industrial and automotive electronics, consumer and computing peripherals.

Your Imagination, Our Innovation Sense - Illuminate - Connect For samples, design kits and whitepapers on these topics, go to: **www.avagoresponsecenter.com/441**

### **Looking Back** First Commercial Ethernet Transeivers

Avago's commitment to, and knowledge of, networking technology goes back to the early days of Ethernet when we pioneered the development of the first commercial Ethernet transceivers.

# Avago Enables 10 PetaFlop Supercomputer with MicroPOD<sup>™</sup> Technology

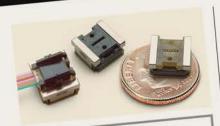

Next-generation computing, switching, and routing systems will require Terabytes of interconnect between nodes. To address higher density applications, Avago has introduced MicroPOD technology, which is a novel parallel optics module with unprecedented density (7.8 mm x 8.2 mm for 12 channels). The 12-channel transmitter and 12-channel receiver modules nominally operate at 10 Gbps per lane (120 Gbps aggregate bandwidth). These modules can be mounted mid-board, thereby eliminating the problem of density constraints caused by having to put connectors at the edge of a board.

### over 5,000 patents and applications

# Avago Introduces 200 Channel SerDes

Avago has successfully developed and delivered complex, high performance ASICs for four decades and established a legacy of embedded SerDes leadership over seven process generations and recently demonstrated 25G and 40Gbps solutions.

recently demonstrated 25G and 40Gbps solutions. Avago's broad range of SerDes is ideal for optical, copper, and backplane applications, offering designers great flexibility. Supporting standards including PCI Express, Fibre-Channel, XAUI, CEI-11G, 10GBASE-KR, and SFI. Avago's SerDes IP meets system designers' needs for both cutting-edge performance and compatibility with legacy backplanes.

Your Imagination, Our Innovation Sense · Illuminate · Connect

Power savings in today's energy-sensitive market is critical. A key differentiator of Avago's SerDes IP is the unique Decision Feedback Equalization (DFE) which results in overall power, as well as area savings. Avago's SerDes cores are steeped in proprietary technology, reflecting deep and ongoing investment in R&D.

### Looking Back

January 2006 Avago ships 25 millionth ASIC embedded SerDes channel for storage, computing and networking applications

Issue 21/2010

www.edn.com

MARIEI

YOU NEED IT

To hack the brain, you need to hack the hardware Pg 9

Signal Integrity: Time invariance Pg 18

Design Ideas Pg 43

Expanding patchwork of state e-waste laws Pg 50

### VOICE OF THE ENGINEER

# A MAGIC TOUCH: THE CONCEPT'S SOUND, BUT IMPLEMENTATION

OPTIONS ABOUND Page 26

POWER ISLANDS CUT POWER AND COSTS IN DEEP-SUBMICRON DESIGNS

Page 21

ESSENTIAL PRINCIPLES FOR PRACTICAL ANALOG BIST

Page 36

## Integrated Device Technology – The Analog and Digital Company

#### INTERFACE & CONNECTIVITY ANALOG & RF

MEMORY & LOGIC CLOCKS & TIMING

Integrated Device Technology is the world leader in silicon timing, serial switching and memory interface solutions. Building on the IDT 30-year heritage and leadership in digital technologies, we have added high-performance analog and system expertise to develop system optimized solutions. IDT: the Analog and Digital Company.

- Memory & Logic

- Interface & Connectivity

- Analog & RF

- Touch & User Interface

- Clocks & Timing

- Audio Products

- Power Management

- Video & Display

Integrated Device Technology

The Analog and Digital Company<sup>™</sup>

For more information visit us online at www.IDT.com

### In need of semiconductors? Digi-Key has the broadest array available today!\*

The industry's broadest product selection available for immediate delivery

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

# ORCAD MAKES IT POSSIBLE BOULEVIEWING GET A NEW PERSPECTIVE ON DESIGN

#### Wouldn't it be helpful if you could view your work in 3D?

OrCAD<sup>®</sup> makes it possible with the new 3D environment in Cadence<sup>®</sup> OrCAD PCB Editor 16.3. See your designs in a whole new dimension. Review collisions, component heights, via structures, and more all in a realistic 3D view that gives you the perspective you need to ensure design closure.

#### Truly scalable PCB technology

Cadence OrCAD PCB design technologies comprise a complete, cost-effective PCB design solution, from design capture to final output. To successfully meet project goals, PCB designers and electrical engineers need powerful, intuitive, and integrated technologies that work seamlessly across the entire PCB design flow. OrCAD PCB design technologies offer fully integrated front-end design, analog/signal integrity simulation, and place-and-route technologies that boost productivity and shorten time to market.

#### **OrCAD** makes it possible

To learn more about the power and productivity gains made possible in the latest OrCAD releases, call EMA Design Automation, a Cadence Channel Partner, at 877.362.3321, e-mail us at info@ema-eda.com, or visit us online at www.ema-eda.com/orcadpossibilities.

cādence°

S 2010 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, and OrCAD are registered trademarks of Cadence Design Systems, Inc. All others trademarks are the property of their respective holders.

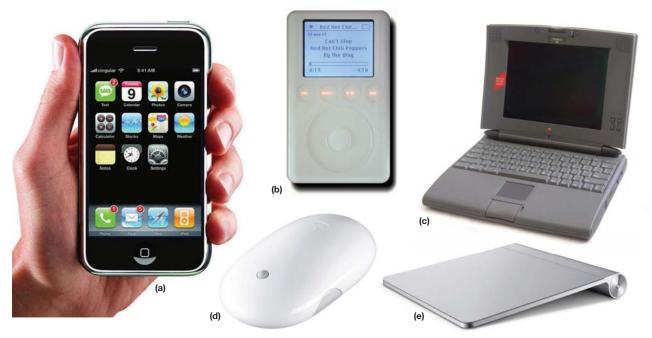

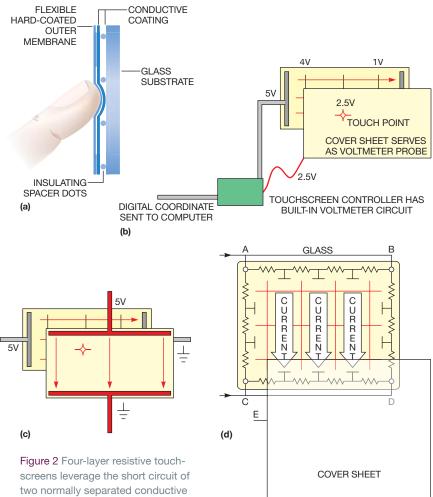

#### A magic touch: The concept's sound, but implementation options abound

26 Touchscreen interfaces are becoming increasingly common, due in part to broader user awareness thanks to the iPhone and its competitors. Technology alternatives have unique mixes of strengths and shortcomings, and assessing the need for multitouch will help you select among them.

by Brian Dipert, Senior Technical Editor

# EDN 11.4.10 contents

21 In the constant drive toward lowering power, the use of power islands may ease your trade-off decisions, but they involve carefully weighing increased costs and complexity.

by Martin Rosicky and Mark Barry, S3 Group

- 12 FloTherm 9 addresses thermal bottlenecks

- 14 Bypass-diode replacement shuts down solar-panel hot spots

- 14 AMD GPUs tout performance as high as 2 TFLOPS

- 14 TI offers free Windows embedded CE 6.0 R3 BSPs

- 15 Wake-up receiver offers 15- to 150-kHz range

- 15 16-bit, 250M-sample/sec ADC serves several applications

- 16 100G-sample/sec real-time scope interleaves ADCs to reduce noise

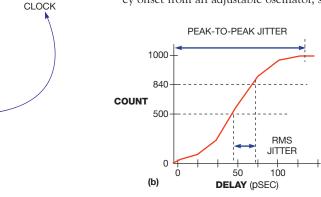

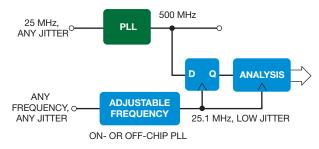

#### 25 MHz, ANY JITTER PIL 500 MHz D Q ANALYSIS FREQUENCY, ANY FREQUENCY, ANY JITTER ON- OR OFF-CHIP PIL

# Essential principles for practical analog BIST

36 Practical analog BIST has the potential to reduce IC-test costs and time to market. by Steve Sunter, Mentor Graphics

# DESIGNIDEAS

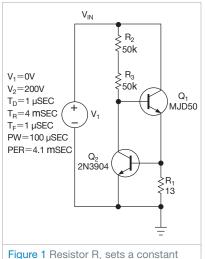

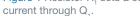

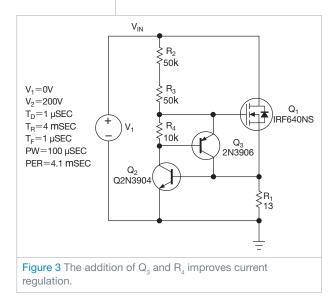

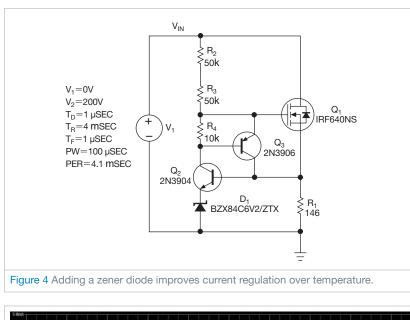

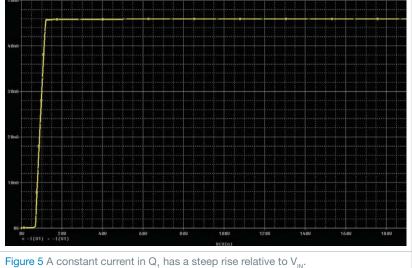

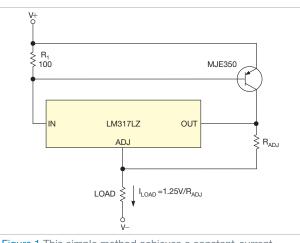

- 43 Circuit achieves constant current over wide range of terminal voltages

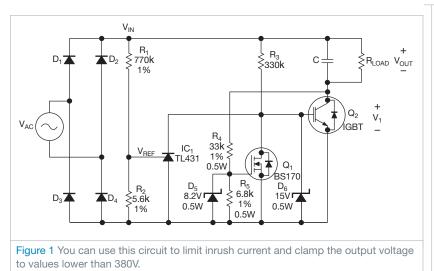

- 44 Limit inrush current in low- to medium-power applications

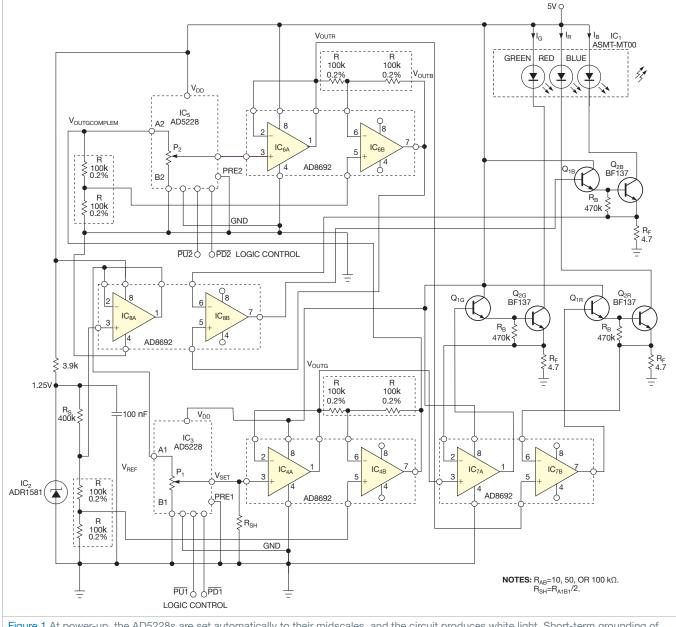

- 6 Electronically tinge white-light source

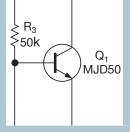

- 48 Transistor boosts regulator current

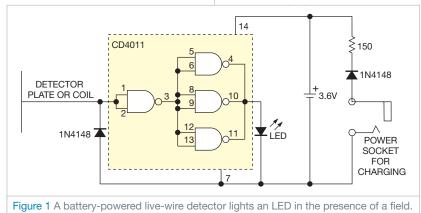

- 8 Detect live ac-mains lines

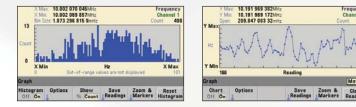

# 2 GHz Clock Generator

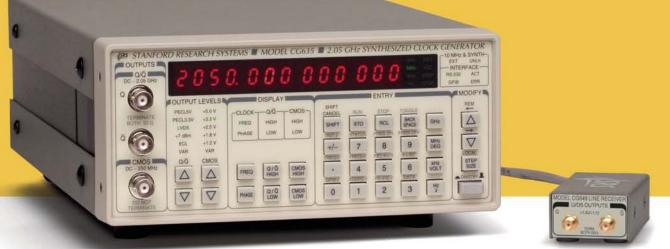

### CG635...\$2490 (U.S. list)

- Square wave clocks from DC to 2.05 GHz

- · Random jitter <1 ps (rms)

- · 80 ps rise and fall times

- · 16-digit frequency resolution

- · CMOS, LVDS, ECL, PECL, RS-485

- · Phase adjustment & time modulation

Plot shows complementary clocks and PRBS (opt. 01) outputs at 622.08 Mb/s with LVDS levels. Traces have transition times of 80 ps and jitter less than 1 ps (rms).

The CG635 generates clock signals — flawlessly. The clock signals are fast, clean and accurate, and can be set to standard logic levels.

*How fast?* Frequency to 2.05 GHz with rise and fall times as short as 80 ps.

*How clean*? Jitter is less than 1 ps and phase noise is better than -90 dBc/Hz (100 Hz offset) at 622.08 MHz.

*How accurate?* Using the optional rubidium timebase, aging is better than 0.0005 ppm/year, and temperature stability is better than 0.0001 ppm.

You would expect an instrument this good to be expensive, but it isn't. You no longer have to buy an rf synthesizer to generate clock signals. The CG635 does the job better—at a fraction of the cost.

# SRS

#### **Stanford Research Systems**

Phone: (408) 744-9040 · Fax: (408) 744-9049 · info@thinkSRS.com · www.thinkSRS.com

### contents 11.4.10

### **DEPARTMENTS & COLUMNS**

9 **EDN.comment:** To hack the brain, you need to hack the hardware

- 18 Signal Integrity: Time invariance

- 50 Supply Chain: Patchwork of state e-waste laws keeps expanding

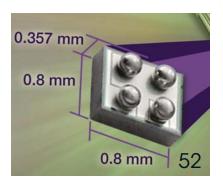

- 52 Product Roundup: Discrete Semiconductors

- 54 Tales from the Cube: Bright lights, big pity

### **EDN** online contents

#### ONLINE ONLY

Check out these Web-exclusive articles:

### ECO-friendly standard-cell design with a dual purpose

Inexpensively change the structure of standard cells in order to use them as capacitors on the original silicon. →www.edn.com/101104toca

#### Building a better memory controller: architectural performance exploration of an AXI memory controller

Early design-space and architecture exploration is critical for memory-controller design. →www.edn.com/101104tocb

#### HID-lighting-technology fundamentals

A better understanding of the fundamentals of HID (high-intensity-discharge) lamps will lead to improvements in the design of the electronic ballast used to power them. ->www.edn.com/101104tocc

#### www.edn.com

# EDN INNO ATION

#### WANTED NOW!

We're accepting nominations for *EDN*'s 21st annual Innovation Awards, which will take place in May 2011.

Don't miss this opportunity for your company's and colleagues' accomplishments to be recognized. The official call for nominations, including step-by-step instructions, is posted here:

www.edn.com/innovation21

EDN® (ISSN#0012-7515) is published semimonthly, 24 times per year, by UBM Electronics, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 310/445-4200; FAX 310/445-4299. Periodicals postage paid at Los Angeles, CA, and at additional mailing offices. SUBSCRIPTIONS— Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. E-mail: EDN@kmpsgrup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing label as well as new address. Allow two months for change, NOTICE—Every precaution is taken to ensure accuracy of content; however, the publisher cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MN 55447. Canada Post: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to Pitney Bowes Inc, PO Box 25542, London, ON NGC 6B2. Copyright 2010 by United Business Media. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 55, Number 21 (Printed in USA).

### Simpler Power Conversion

IR's SmartRectifier<sup>™</sup> chipset for AC-DC power converters dramatically simplifies design and improves efficiency.

SmartRectifier<sup>™</sup> ICs

| Part<br>Number                 | IR1166<br>SPBF     | IR1167A<br>SPbF | IR1167B<br>SPbF | IR1168<br>SPbF | IR11662<br>SPbF | IR11672A<br>SPbF | IR11682<br>SPbF |  |

|--------------------------------|--------------------|-----------------|-----------------|----------------|-----------------|------------------|-----------------|--|

| Package                        | S0-8               |                 |                 |                |                 |                  |                 |  |

| V <sub>cc</sub> (V)            | 20                 |                 |                 |                |                 |                  |                 |  |

| V <sub>fet</sub> (V)           | 200                |                 |                 |                |                 |                  |                 |  |

| Sw Freq.<br>max (kHz)          | 500                |                 |                 |                |                 |                  | 400             |  |

| Gate Drive<br>±(A)             | +1/-4              | +2,             | +1/-4           | +1/-4          | +2/-7           | +1/-4            |                 |  |

| V <sub>GATE</sub><br>Clamp (V) | 10.7               | 10.7            | 14.5            | 10.7           | 10.7            | 10.7             | 10.7            |  |

| Min. On<br>Time (ns)           | Program. 250 -3000 |                 |                 | 750            | Program         | 850              |                 |  |

| Enable Pin                     | Yes                | Yes             | Yes             | No             | Yes             | Yes              | No              |  |

| Channel                        | 1                  |                 |                 | 2              | 1               |                  | 2               |  |

| Automatic<br>MOT<br>Protection | No                 | No              | No              | No             | Yes             | Yes              | Yes             |  |

For more information call 1.800.981.8699 or visit www.irf.com

### MachXO. THE ALL-IN-ONE PLD.

**Do more with the most versatile, non-volatile PLD for low-density applications.** Loaded with flexible user I/Os, embedded memory, PLLs, and more—now you have the freedom to create and design with a single, easy-to-use, instant-on, and secure PLD.

Discover all you can do with the MachXO PLD family at: latticesemi.com/machxo

Lattice Semiconductor, #703, 704 Prestige Meridien-II, No. 30, M.G. Road, Bangalore-560001 INDIA, Tel: +91-80-4095 2233

©2009 Lattice Semiconductor Corporation. All rights reserved. Lattice Semiconductor Corporation, L (& design), Lattice (& design), MachXO and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries, in the United States and/or other countries. Other marks are used for identification purposes only, and may be trademarks of other parties.

EDN.COMMENT

#### BY MARGERY CONNER, TECHNICAL EDITOR

# To hack the brain, you need to hack the hardware

he human body—especially the brain—may be the final frontier for hackers. The same curiosity that drives users to open applications, see what makes them tick, and then improve or repurpose them is even more relevant for the brain. Equipment to monitor the brain and its responses is expensive, limiting research into BCIs (brain-to-computer interfaces) to academia and medical research. However, the gaming market, in which thought control of games is a novel gimmick, is driving the appearance of BCI devices at prices far lower than the tens of thousands of dollars you can expect to pay for medical-research-quality EEG (electroencephalography), which records the electrical activity along the scalp that the firing of neurons within the brain produces. (For more on BCIs, see next issue's cover story, "Brain-tocomputer-interface hardware moves from the realm of research.")

> type of

A new headset, the Emotiv Epoc, sells for approximately \$300 and is simple to use: Pull it from the box, connect it to your PC, place it on your head, spend a few moments on the canned exercises that let the headset algorithms learn your brain-wave pattern, and you can begin manipulating virtual images on your PC with your brain. With this gear, it becomes feasible to hack your own brain.

The headset combines hardware and sophisticated algorithms that analyze and interpret the tiny EEG voltages. According to Emotiv founder Tan Le at a recent TED (technology/entertainment/design) conference, the folds of a brain present a significant challenge in interpreting the signals because each person's brain has a different folding pattern. "Even though a signal comes from the same functional part of the brain," she says, "by the time the structure has been folded, its physical location differs among individuals, even identical twins." Emotiv created an algorithm that "unfolds" the cortex to map the signal closer to its source and make it able to work across a mass population.

The device's simplicity impressed hacker Cody Brocious, who solicited for donations in the hacker community and quickly raised the funds to buy a headset. He discovered the key to the encrypted data coming over the USB (Universal Serial Bus) connection and built a decryption routine. So far, his library of code hacks to the device just pulls raw data from the unit; it can't filter the signals or tell which sensor corresponds to each data stream. Brocious created Cody's Emokit project, an open-source library for reading data directly from the headset, and posted research about his project on the Emotiv user forum, which the company runs (**Reference 1**).

Emotiv officials didn't like the fact that Brocious cracked the encryption and posted his library, claiming that doing so could force the company out of business (**Reference 2**). Emotiv sells a \$700 developers' version of the headset that allows access to the data, but it is not an open environment; the company controls access. Apparently, the company is working to close the encryption hole and end the project.

Emotiv must choose whether and how to protect its business model. It might do well to take a look at a recent announcement from Amazon about its creation of an app store for Android phones (Reference 3). Amazon sees how lucrative the growing market is for apps that run on the open Android standard-perhaps more profitable than selling the phone itself. Emotiv could be better off in opening the headset interface and encouraging the headset as an open-standard platform. Besides the elegance of the headset, the company's secret sauce seems to be filtering algorithms, which would not be part of an open hardware interface.EDN

#### REFERENCES

Emokit. GitHub Social Coding, http:// bit.ly/b1W09O.

"Raw Emotiv signals encryption hacked on consumer headset," http:// bit.ly/crLtgO.

Kane, Yukari Iwatani, and Geoffrey A Fowler, "Amazon Amps Up Apps Rivalry," *The Wall Street Journal*, Oct 7, 2010, http://bit.ly/axtym6.

### "I never expected a frequency counter to do so much,

# Speed, resolution and accuracy are just the beginning.

Especially today, every investment you make has to earn its keep, and RF/ Universal Frequency Counters are no exception. The new Agilent 53200A Series boasts greater performance than anything in its class, along with important extras that may surprise you. Like a large color display for built-in analysis, unprecedented connectivity and new measurement capabilities. You get more than higher performance. You get insight. That's Agilent.

so fast."

| NEW! | 53200 Series RF/Universal Frequency Counters |                                                                                                                                                    |  |  |  |  |  |  |

|------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|      | 53210A                                       | 350 MHz, 10 digit/s, RF Frequency Counter                                                                                                          |  |  |  |  |  |  |

|      | 53220A                                       | 350 MHz, 12 digit/s, 100 ps, Universal Frequency Counter / Timer                                                                                   |  |  |  |  |  |  |

|      | 53230A                                       | 350 MHz, 12 digit/s, 20 ps, Universal Frequency Counter / Timer with continuous/<br>gap-free and optional pulse microwave measurement capabilities |  |  |  |  |  |  |

Agilent and our Distributor Network Right Instrument. Right Expertise. Delivered Right Now.

800-463-9275 www.newark.com/agilent Get 10% off the 53230A (limited time only\*) Register to receive free measurement hints www.newark.com/Agilent\_Counters

# EDN

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt 1-781-869-7982; russell.pratt@cancom.com

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes

1-925-736-7617; judy.hayes@cancom.com

EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson Test and Measurement, DFx 1-781-869-7970; richard.nelson@cancom.com

#### MANAGING EDITOR

Amy Norcross Contributed technical articles 1-781-869-7971; amy.norcross@cancom.com

#### MANAGING EDITOR-NEWS

Suzanne Deffree Electronic Business, Distribution 1-631-266-3433; suzanne.deffree@cancom.com

#### SENIOR TECHNICAL EDITOR

Brian Dipert Consumer Electronics, Multimedia, PCs, Mass Storage 1-916-548-1225; brian.dipert@cancom.com

#### TECHNICAL EDITOR

Margery Conner Power Sources, Components, Green Engineering 1-805-461-8242; margery.conner@cancom.com

#### TECHNICAL EDITOR Mike Demler EDA, IC Design and Application michael.demler@cancom.com

TECHNICAL EDITOR Paul Rako Analog, RF, PCB Design 1-408-745-1994; paul.rako@cancom.com

#### DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World

edndesignideas@cancom.com SENIOR ASSOCIATE EDITOR Frances T Granville

1-781-869-7969; frances.granville@cancom.com

#### ASSOCIATE EDITOR

Jessica MacNeil 1-781-869-7983; jessica.macneil@cancom.com

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg strassbergedn@att.net Nicholas Cravotta editor@nicholascravotta.com Robert Cravotta robert.cravotta@embeddedinsights.com

> CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology edn.editor@cancom.com

#### COLUMNISTS Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

LEAD ART DIRECTOR Marco Aguilera

ASSOCIATE ART DIRECTOR Tim Burns

#### **PRODUCTION** Michael Ciardiello,

Michael Clardiello, Director of Premedia Technologies Jeff Tade, Production Director Brian Wu, Publications Production Manager Jeff Polman, Derric Treece, Senior Production Artists William Baughman, Lucia Corona Ricardo Esparza, Production Artists

#### **EDN EUROPE** Graham Prophet, Editor, Reed Publishing

gprophet@reedbusiness.fr

#### EDN ASIA

Wai-Chun Chen, Group Publisher, Asia waichun.chen@cancom.com Kirtimaya Varma, Editor-in-Chief kirti.varma@cancom.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director william.zhang@cancom.com Jeff Lu, Executive Editor jeff.lu@cancom.com

#### EDN JAPAN Katsuya Watanabe, Publisher katsuya.watanabe@cancom.com Ken Amemoto, Editor-in-Chief ken.amemoto@cancom.com

EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change.

UBM Electronics, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

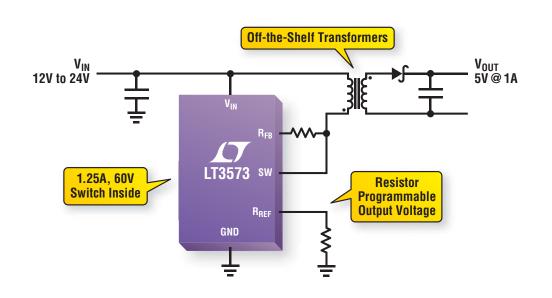

### HIGH-EFFICIENCY SWITCHING REGULATOR

United States Postal Sevice Statement of Ownership, Management, and Circulation (Requester Publications Only)

1. Publication Title: EDN 2. Publication Number: USPS 074-090 3. Filing Date: October 1, 2010 4. Issue Frequency: Semi-Monthly 5. No. of Issues Published Annually: 24 6. Annual Subscription Price: \$150 US, Canada, Mexico 7. Complete Mailing Address of Known Office of Publication: Canon Communications LLC, 11444 W. Olympic BMd., Los Angeles, CA 90064 9. Full Names and Complete Mailing Address of Publicsher: Canon Communications LLC, 11444 W. Olympic BMd., Los Angeles, CA 90064 9. Full Names and Complete Mailing Address of Headquarters or General Business Office of Publicsher: Canon Communications LLC, 11444 W. Olympic BMd., Los Angeles, CA 90064 9. Full Names and Complete Mailing Address of Headquarters or General Business Office of Publisher: Russell E Pratt, Editor. Rick Nelson, Managing Editor. Amy Norcross, Canon Communications LLC, 31444 W. Olympic BMd., Los Angeles, CA 90064 9. Full Names Address of Headquarters LL, 33 Hayden Au, Lexington, MA 02421 10. Owner: Canon Communications LLC, 11444 W. Olympic BMd., Los Angeles, CA 90064 11. Known Bondholders, Mortgages, and Other Security Holders Owning or Holding 1 Percent or More of Total Annount of Bonds, Mortgages, or Other Securities: None 12. (Must be completed if the publication title shown in item 1 is a publication published and owned by a non-profit organization.) The purpose, function and nonprint Status of this organization and the earning thatus of this organization and the earning thatus of the singerization and the earning thatus of this organization and the earning theorem tax purposes: Has Not Changed During Preceding 12 Months 13. Publication: EDN 14. Issue Date for Circulation Data: September 9, 2010

| 15. Extent and Nature of Circulation:                                                                                                                                                                                                                                                          | verage No. Copies<br>Each Issue During<br>ceding 12 Months | No. Copies of Single<br>Issue Published<br>Nearest to Filing Date |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| a. Total Number of Copies (Net Press Run)                                                                                                                                                                                                                                                      | 114,630                                                    | 114,568                                                           |  |  |  |  |

| b. Legitimate Paid and/or Requested Distribution (by Mail or Outside the Mail)                                                                                                                                                                                                                 |                                                            |                                                                   |  |  |  |  |

| <ol> <li>Individual Paid/Requested Subscriptions Stated on PS Form 3541. (Include direct written request from the re<br/>telemarketing and internet request from recipient, paid subscriptions, including nominal rate subscriptions,<br/>tiser's proof copies and exchange copies)</li> </ol> |                                                            | 83,374                                                            |  |  |  |  |

| 2. Copies requested by Employers for Distribution to Employees by Name or Position Stated on PS Form 3541                                                                                                                                                                                      | 0                                                          | 0                                                                 |  |  |  |  |

| <ol> <li>Sales Through Dealers and Carriers, Street vendors, Counter Sales and Other Paid or Requested Distributuion (<br/>USPS</li> </ol>                                                                                                                                                     | Dutside 30,164                                             | 30,100                                                            |  |  |  |  |

| 4. Requested Copies Distributed by Other Mail Classes Through the USPS (eg First-Class Mail)                                                                                                                                                                                                   | 0                                                          | 0                                                                 |  |  |  |  |

| c. Total Paid and/or Requested Circulation (Sum of 15b (1), (2), (3) and (4))                                                                                                                                                                                                                  | 113,519                                                    | 113,474                                                           |  |  |  |  |

| d. Nonrequested Distribution (By Mail and Outside the Mail) Free                                                                                                                                                                                                                               |                                                            |                                                                   |  |  |  |  |

| 1. Outside County Nonrequested Copies Stated on PS Form 3541                                                                                                                                                                                                                                   | 384                                                        | 458                                                               |  |  |  |  |

| 2. In-County Nonrequested Copies Stated on PS Form 3541                                                                                                                                                                                                                                        | 0                                                          | 0                                                                 |  |  |  |  |

| <ol> <li>Nonrequested Copies Distributed Through the USPS by Other Classes of Mail (eg First-Class Mail, Nonrec<br/>copies mailed in excess of 10% Limit mailed at Standard Mail or Package Service Rates)</li> </ol>                                                                          | juestor 0                                                  | 0                                                                 |  |  |  |  |

| <ol> <li>Nonrequested Copies Distributed Outside the Mail (include Pickup Stands, Trade Shows, Showrooms and<br/>Source)</li> </ol>                                                                                                                                                            | i Other 99                                                 | 0                                                                 |  |  |  |  |

| e. Total Nonrequested Distribution (Sum of 15d (1), (2) and (3))                                                                                                                                                                                                                               | 483                                                        | 458                                                               |  |  |  |  |

| f. Total Distribution (Sum of 15c and e)                                                                                                                                                                                                                                                       | 114,002                                                    | 113,932                                                           |  |  |  |  |

| g. Copies Not Distributed (see Instructions to Publishers #4 (page 3))                                                                                                                                                                                                                         | 628                                                        | 636                                                               |  |  |  |  |

| h. Total (Sum of 15f and g)                                                                                                                                                                                                                                                                    | 114,630                                                    | 114,568                                                           |  |  |  |  |

| i. Percent Paid and/or Requested Circulation (15c divided by f times 100)                                                                                                                                                                                                                      | 99.58%                                                     | 99.60%                                                            |  |  |  |  |

| 16. Publication of Statement of Ownership for a requester Publication is required and will be printed in the November 4, 2010, issue of this publication.                                                                                                                                      |                                                            |                                                                   |  |  |  |  |

| 17. Signature and Title of Editor, Publisher, Business Manager, or Owner: Russell E Pratt, Publisher, September 9, 2010                                                                                                                                                                        |                                                            |                                                                   |  |  |  |  |

I certify that all information furnished on this form is true and complete. I understand that anyone who furnishes false or misleading information on this form or who omits material or information requested on the form may be subject to criminal sanctions (including fines and imprisonment) and/ or civil sanctions (including with penalties).

# EDITED BY FRAN GRANVILLE

#### **INNOVATIONS & INNOVATORS**

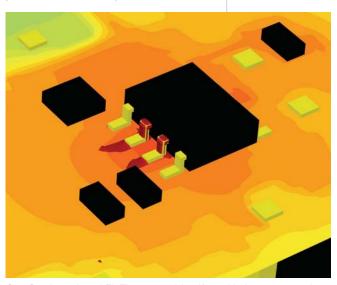

# FloTherm 9 addresses thermal bottlenecks

Mentor Graphics has announced its next-generation FloTherm 3-D CFD (computational fluid-dynamics) software for electronics-cooling applications. Erich Bürgel, general manager of Mentor's mechanical-analysis division, says that the patent-pending technology in the FloTherm 9 software provides Bn (bottleneck) and Sc (short-cut) fields so that, for the first time, engineers can identify where and why heat-flow congestion occurs in electronic design. The software also identifies thermal short cuts to help quickly resolve design problems.

The Bn and the Sc fields convert the software from an observation tool, which identifies heatmanagement problems, to an effective thermal-design-problem-solving tool that suggests potential solutions to the designer. Bürgel says that CamSemi (www.camsemi.com) has used the software as a thermal-design tool.

According to Nigel Heather, vice president of engineering at CamSemi, FloTherm 9 saved the company time and cost when developing an IC for a new generation of Energy Starcompliant mobile-phone chargers. "The baseline simulation using the bottleneck feature quickly highlighted a potential thermal issue, and further iterations confirmed our solution," he says. "To achieve the same result by building prototype boards would have taken a long time and drawn resources away from other critical work."

Bürgel explains that the Bn field shows where in a design the heat path is being congested as it attempts to flow from highjunction-temperature points to the ambient. Design changes to these bottlenecks can help solve the heat-flow problem. The Sc field highlights possible approaches, in which the addition of a simple element, such as a gap pad or chassis extrusion, provides a new effective heat-flow path to further cool the system.

FloTherm 9 supports the importing of XML (Extensible Markup Language) model and geometry data to enable the integration of FloTherm into data flows. Version 9 also has a direct interface to the Mentor Graphics Expedition PCB (printed-circuit-board)-design platform. The direct interface enables users to import native Expedition PCB data and delete or edit additional objects, such as heat sinks, thermal vias, board cutouts, and electromagnetic cans, for more accurate thermal-model-design development. **—by Rick Nelson > Mentor Graphics**, www.mentor.com/ products/mechanical/products/flotherm.

#### **TALKBACK**

"The lawmakers run strictly on emotion and appealing to the masses without a lot of facts getting in the way. It has been that way for quite a few years, and I really don't see any means of changing it."

-Engineer and writer William Ketel, in *EDN's* Talkback Section, at http://bit.ly/cWTl4M. Add your comments.

CamSemi employed FloTherm 9 to identify and help overcome thermal bottlenecks when it designed an IC for a mobile-device charger.

### Remote manageability and security built in. The express lane is now open.

**Intelligence where you need it.** The Intel® Core™ processor with vPro™ technology lets you fast forward to the next generation of transaction devices with advanced management and protection capabilities. Get moving with the developer's playbook at **intel.com/embedded/intelligence**

# pulse

# Bypass-diode replacement shuts down solar-panel hot spots

Solar panels usually find use in multiple-unit configurations – whether on residential rooftops with a dozen panels or a utility solar farm with thousands of panels. These arrays need protection from panel failures or shading; otherwise, 8 to 12A in a string of panels has nowhere to go.

Panels traditionally rely on a simple bypass diode to shunt current around a failed panel. STMicroelectronics has introduced a more sophisticated controller-switch SIP (system in package), which replaces the bypass diode with a more intelligent device. The SPV1001 contains a low-loss power switch and a precision controller and eliminates almost all of

The SPV1001 contains a low-loss power switch and a precision controller and eliminates almost all of the energy each diode loses when the panel is producing energy and the diode is in its off state.

the energy each diode loses when the panel is producing energy and the diode is in its off state. For example, reverseleakage current at 40V reverse voltage is 1  $\mu$ A at 25°C and 20  $\mu$ A at 125°C. The forward-voltage drop at a forward current of 8A is 70 and 160 mV at 25 and 125°C, respectively.

The device comprises a power MOS transistor that charges a capacitor during the off time and drives its gate during the on time with the charge it previously stored in the capacitor. On and off times reduce the average voltage drop across the drain and source terminals and thus their power dissipation. The SPV1001 sells for approximately \$3 (1000), depending on the package.

-by Margery Conner

STMicroelectronics,

www.st.com.

# AMD GPUs tout performance as high as 2 TFLOPS

MD (Advanced Micro Devices) has unveiled the first two members of its second-generation DX11-supportive family, the Radeon HD 6000 series of GPUs (graphics-processing units). Both the HD 6850 and 6870 use a 40-nm process and have 1.7 billion transistors. Engine clocks run at 725 and 900 MHz, respectively, and computation performance is 1.5 and 2 TFLOPS (trillion floating-point operations/sec), respectively. The 6850 has 960 system processors, and the 6870 has 1120, and peak power con-

sumption is 127 and 151W, respectively.

The 6850 sells for \$179 in board form with a 1-Gbyte frame buffer. The 6870 sells for \$229, also with 1 Gbyte of GDDR5 (graphics double-data-rate 5) SDRAM. Both chips interface to their frame-buffer memory arrays over a 256-bit bus and embed a dual DVI and a dual mini DisplayPort interface, along with an HDMI (high-definition-multimedia-interface) port. The 6870-based boards require two six-pin power connectors; the 6850 boards require only one. **—by Brian Dipert ▷AMD**, www.amd.com.

#### TI OFFERS FREE WINDOWS EMBEDDED CE 6.0 R3 BSPs

**Texas Instruments has** introduced Microsoft Windows Embedded CE 6.0 R3 BSPs (boardsupport packages) for OMAP (open multimedia applications platform)-L1x floating-point DSP and ARM9 processors, Sitara AM1x ARM9 microprocessors, and associated evaluation modules. For OMAP-L1x, the BSP provides access to TI's TMS320C674x DSP using **DSP/BIOS Link interpro**cessor-communication software, enabling you to develop algorithms using CE 6.0 R3. Download these BSPs from www. ti.com/wincebsp-prtf.

The OMAP-L1x and AM1x BSPs are compatible with the OMAP-L137, OMAP-L138, AM1707, and AM1808 proces sors; the AM17x, AM18x, and OMAP-L138/ TMS320C6748 evaluation modules; the AM18x and OMAP-L138 experimenter's kits; and the OMAPL137/C6747 floating-point starter kit. TI plans to expand its list of Windows CE-supported product lines. These products will include the Sitara AM3517 and AM3505, the DaVinci DM644x video processors, and several OMAP35x devices. CE 6.0 **R3 BSPs for OMAP-L1x** and AM1x devices are available at www.ti.com/ wincebsp-prtf.

-by Rick Nelson Texas Instruments, www.ti.com.

16-BIT, 250M-SAMPLE/SEC ADC SERVES SEVERAL APPLICATIONS

02

Analog Devices' new 16-bit, input-buffered AD9467 pipeline ADC can attain an SNR (signal-to-noise ratio) of 76.4 dB full-scale and an SFDR (spurious-free dynamic range) of 100 dB full-scale. The device operates from 1.8 and 3.3V rails and consumes 1.32W when operating at 250M samples/sec. Jitter is 60 fsec rms. It has LVDS (low-voltagedifferential-signaling) outputs on eight multiplexed pairs of pins providing the 16-bit output. The ADC suits use in military radar, data-acquisition systems, cell-phone base stations, power-amplifier linearization, infrared imaging, and antenna-array positioning. The differential analog input has 3.5-pF equivalent input capacitance and 530Ω input resistance. You can program the full-scale input range at 2 to 2.5V, alving a trade-off between SNR and SFDR. Analog **Devices provides behav**ioral models of the device that reproduce errors associated with both static and dynamic features

The part comes in 72pin LFCSPs, operates over a -40 to +85°C temperature range, and has a suggested retail price of \$120 (1000). The AD0467-250EBZ evaluation board costs \$300.

-by Paul Rako Analog Devices, www.analog.com.

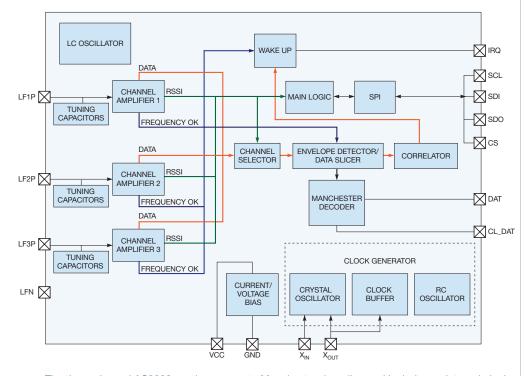

# Wake-up receiver offers 15- to 150-kHz range

A ustriamicrosystems has introduced the three-channel AS3933 low-frequency receiver, which enables battery-powered systems to add remotewake-up capability. It offers a sensitivity of 80  $\mathbb{N}$ V rms with current consumption of only 2.7  $\mathbb{N}$ A to extend battery life.

Featuring a receiver frequency range of 15 to 150 kHz, the AS3933 can serve applications including active RFID, high-value asset tracking, real-time-location systems, operator identification, wireless sensor networks, and access control or remote keyless entry.

The AS3933 provides a digital RSSI (received-signalstrength-indicator) value for each active channel, and it supports a programmable data rate and Manchester decoding with clock recovery. It also includes an internal clock generator derived from either a crystal oscillator or the internal RC oscillator. According to the company, it is the first such device to provide a built-in automatic antenna tuner that tunes the antenna to the desired carrier frequency. Customers frequently request this feature to reduce their BOM (bill-of-materials) costs without compromising cost.

The programmable features of the AS3933 allow optimized settings for longer operating distance and retain reliable wake-up generation. You can adjust the AS3933's sensitivity level in the presence of a strong RF field or in noisy environments. The automatictuning feature ensures perfect matching to the desired carrier frequency, simplifying antenna tuning.

The AS3933 also features reliable 1-, 2-, or 3-D wakeup-pattern detection and supports wake-up without pattern detection. It has an adjustable sensitivity level, is resistant to false wake-ups, and has a false-wake-up counter. Dynamic range is 64 dB, and it operates from a supply voltage of 3.4 to 3.6A at an ambient temperature of 25°C.

The AS3933 operates with a 3V power supply and over the -40 to  $+85^{\circ}$ C temperature range. The device is available in 4×4-mm, 16-pin TSSOP and 16-pin QFN packages. The price is \$2.60 (1000), and a demonstration board is also available.

–by Rick Nelson

Austriamicrosystems, www.austriamicrosystems. com.

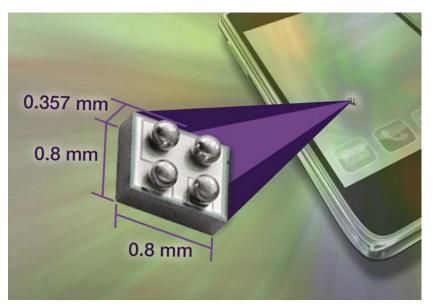

The three-channel AS3933 receiver supports Manchester decoding and includes an internal clock generator derived from either a crystal oscillator or the internal RC oscillator.

# pulse

# 100G-sample/sec real-time scope interleaves ADCs to reduce noise

ektronix has announced the DPO (digital-phosphor-oscilloscope), DSA (digital-signal analyzer), and MSO (mixed-signal-oscilloscope) 70000C series, which simultaneously capture 100G samples/sec on two channels or 50G samples/sec on four channels. The higher sampling rate yields lower noise and increased numbers of data points on five-times-oversampled 20-GHz waveforms. MSO models also include 16 logic-timing-analysis channels that each acquire 12.5G samples/sec.

According to the company, the five-times oversampling is the highest of any high-bandwidth real-time scope. It delivers significant benefits, including more accurate signal-integrity

measurements for such high-speed serial standards as PCle (Peripheral Component Interconnect Express) 3. Other enhancements include a faster computing platform and a more stable timebase, ideal for radar applications.

You can use high-performance oscilloscopes with bandwidths greater than 4 GHz in a variety of high-speed-serial, wideband-radar, fast-opticalcommunications, highend embedded-system, and high-energy-physics applications. As designs move to everhigher data rates, the measurement system's margin becomes increasingly critical. The new series delivers the performance and signal fidelity designers need to ensure that their latest components and systems meet design specifications.

Besides the twofold increase in sampling rate compared with the B series it replaces, the C series features a computing platform that offers faster processing of longer data records, such as those in jitter, noise, and BER (bit-error-rate) measurements and statistics. Booting and application start-up are also significantly quicker.

In any digital oscilloscope, there is a strong correlation between sampling rate and internal noise. A high sampling rate results in less noise, which in turn increases the user's margin. Extensive comparison testing shows that the C series operating in the 100G-sample/ sec, two-channel mode delivers as much as 20% less noise than does the same instrument operating in the 50G-sample/ sec, four-channel mode. tion characteristics from pulse to pulse is key to the system's operation. High-performance oscilloscopes are the tools of choice for radar-pulse measurement but must have a stable timebase that stavs on frequency for long captures. The DPO/DSA/MSO70000C series meets this requirement with a new high-stability timebase that reduces long-term jitter, phase, and frequency instability. With the pulse- and frequency-settling-measurement capabilities of Tektronix's SignalVu vector-signal-analysis software, the C series enables designers of frequency-agile radios and radars to accurately verify system performance.

The DPO/DSA/MSO70000C scopes provide the bandwidth and sampling rates for debugging serial-data signals to 12

Most high-performance real-time digital scopes gain bandwidth when they interleave pairs of channels' ADCs and capture memory to double the sampling rate. The units in the 70000C series, such as this 20-GHz-bandwidth MSO72004C, in contrast, gain time resolution and SNR (signal-to-noise ratio).

Modern radar designs use frequency and phase modulation within the radar pulses to improve range-resolution and target-identification capabilities. Maintaining the same modulaGbps on all four channels simultaneously—ideal for multilane applications, including PCIe 3, SATA (serial advanced-technology attachment), 6-Gbps SuperSpeed USB (Universal Serial Bus), HDMI (high-definition multimedia interface), DisplayPort, and 10-Gbps Ethernet. The FastAcq acquisition mode provides a capture rate greater than 300,000 waveforms/sec—about 100

Probing accessories enable both analog and digital connections to the device under test with minimal disruption.

times as fast as competing alternatives—delivering both critical insight into signal behavior and in-depth analysis.

Tektronix offers a range of software packages for high-

speed serial-data design, debugging, and compliance verification. These packages include DPOjet for jitter and timing analysis: SDLA (serial-data-link analysis) for testing transmitters, interconnects, and receivers: and standard-specific packages for DDR, DisplayPort, PCIe, USB, HDMI, SATA, Ethernet, Fibre Channel, and others. In addition. Tektronix delivers a variety of oscilloscope probing accessories, includ-

ing TriMode probes, for making both analog and digital connections to the device under test with minimal disruption. US prices for the DPO/DSA/ MSO70000C series start at \$110,000 for a 12.5-GHzbandwidth DPO71254C.

—by Dan Strassberg

►Tektronix Inc,

www.tek.com.

# Analog Devices: enabling the designs that make a difference in people's lives

signostics

ADI helps Signostics deliver portable ultrasound imaging quickly and affordably with their new personal ultrasound system.

At ADI, continuous innovation in signal processing technologies makes possible the design of sophisticated medical diagnostic and monitoring systems, as well as health and wellness devices relied on by care providers and patients around the globe. We're pioneering technologies that hold the promise of accurate, affordable home monitoring and assistance for heart health, high blood pressure, diabetes, and patient activity. For 40 years, engineers have relied on our analog and mixed-signal ICs to set performance standards and on our people for their system expertise. This tradition continues. Explore ADI healthcare solutions at: *www.analog.com/healthcare.*

SIGNAL INTEGRITY

61

#### BY HOWARD JOHNSON, PhD

### Time invariance

ccording to the Western science you value so highly, time itself eventually comes to an end," said my friend Chris "Breathe" Frue, a talented musician and audio technician who wants to learn more about equalizers, a subject pertaining to both audio and high-speed digital systems. "Nothing can remain time-invariant for *all time*."

"Maybe it would help to look at a circuit that is *not* time-invariant," I replied. "Let's say the power-supply ripple-filter capacitors in an old tube amplifier were to dry out and start to fail. The dc-power voltage available to the tubes would develop large, 60-cycle undulations. You would probably hear a lot of hum in the output."

"My old keyboard amp did that," said Breathe.

I continued, "Besides the hum, the gain of the amplifier actually varies, along with the 60-cycle variations in power voltage, causing a high-speed tremolo effect. A quick experiment to measure the gain on just 10 cycles of a 4000-Hz burst would return different results depending on precisely where within the 60-cycle hum pattern the experiment began. In contrast, a timeinvariant system behaves the same regardless of when, within a reasonable span of time, you begin your experiment. Even if the time-invariant system already produces a certain amount of inherent delay, if you delay the input by a certain time, you delay the output by that much more."

In response to Breathe's request for an example, I said, "A hard-limiting, or clipping, function is perfectly time-invariant. It distorts your signal through an instantaneous process that happens point by point. Time doesn't matter."

"So, a good amplifier with no hum would be time-invariant?" he asked.

"Pretty much," I answered. "Two key properties we look for in any audio system are superposition and time invariance [**Reference 1**]. Given those properties, the system can process any combination of signals, at any time, just as well as an individual signal."

Breathe knit his brow. "You said 'just

as well as.' That sounds like an important caveat."

"It is," I agreed. "What processes do you know so far that obey superposition and time invariance?"

"Well, the clipping function you just mentioned is time-invariant but does not obey superposition," he said. "A tremolo circuit probably obeys superposition but varies its gain with time. The only process I know that satisfies both properties is a simple scaling factor."

"One other process," I replied, "satisfies both properties: a time delay. Think about it. Scaling and delay, and linear combinations of different amounts of scaling and delay, are the only things you can do that obey both superposition and time invariance. These simple operations form the basis of almost all forms of equalization."

"Delay and scaling are such simple operations," said Breathe. "Isn't that restrictive?"

"It's wonderfully restrictive," I answered. "The requirements of time invariance, coupled with superposition, weed out a tremendous number of ineffective functions, leaving the rich array of possible system operations generally known as linear operations, or, more precisely, linear-time-invariant operations. For example, take signal x(t) and subtract from it a slightly delayed version of the same signal." On a paper napkin, I wrote  $y(t)=x(t)-x(t-\Delta t)$ .

Staring at the napkin, Breathe said, "That looks like the definition of the time-derivative from calculus."

"Yes, it does," I said. "For small values of  $\boxtimes t$  (change in time), it looks almost exactly the same. The time-derivative operator from calculus and the act of integration over time are both linear, time-invariant processes. Integration is just a cumulative, running sum of previous values of a signal. So scaling, delay, differentiation, and integration are the basic processes that are both linear and time-invariant."

"If I remember my circuit theory correctly, a typical passive, linear circuit comprises a bunch of derivative and integration operations all mixed together," said Breathe. "Does this mean that all passive, linear electronic circuits are linear-time-invariant processes?"

"You got it!" I answered. "All passive, linear circuits do the 'same thing." They just apply some linear-time-invariant process to the input signal. The big questions are, Which processes do they apply? And how do we characterize what those processes do?"EDN

#### REFERENCE

Johnson, Howard, "Linear superposition," *EDN*, Oct 7, 2010, pg 21, http://bit.ly/bOXC7g.

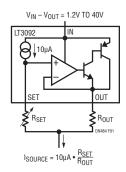

### Convert Temperature to Current at High Linearity with LT3092 Current Source – Design Note 484

Todd Owen

#### **Electronics 101**

One of the first lessons in a basic electronics course covers the symbols for resistors, capacitors, inductors, voltage sources and current sources. Although each symbol represents a functional component of a real-world circuit, only some of the symbols have direct physical counterparts. For instance, the three discrete passive devices—resistors, capacitors, inductors—can be picked off a shelf and placed on a real board much as their symbolic analogs appear in a basic schematic. Likewise, while voltage sources have no direct 2-terminal analog, a voltage source can be easily built with an offthe-shelf linear regulator.

The black sheep of basic electronics symbols has long been the 2-terminal current source. The symbol shows up in every basic electronics course, but Electronics 101 instructors must take time to explain away the lack of a real-world equivalent. The symbol presents a simple electronics concept, but building a current source has, until now, been a complex undertaking.

#### A Real 2-Terminal Current Source

With the introduction of the LT®3092, it is now as easy to produce a 2-terminal current source as it is to create a voltage source. Figure 1 shows how the LT3092 uses an internal current source and error amplifier, together with the ratio of two external resistors, to program a constant output current at any level between 0.5mA and 200mA.

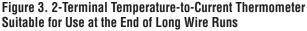

Figure 1. 2-Terminal Current Source Requires Only Two Resistors to Program

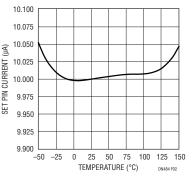

The flat temperature coefficient of the internal reference current (highlighted in Figure 2) is as good as many voltage references. Low TC resistors do not need to be used; the temperature coefficients of the external resistors need only match one another for optimum results.

No frequency compensation or supply bypass capacitors are needed. Frequency compensation is internal and the internal reference circuitry is buffered to protect it from line changes.

No input-to-output capacitors are required. While extensive testing has been done to ensure stable operation under the widest possible set of conditions, complex load impedance conditions could provoke instability. As such, testing in situ with final component values is highly recommended. If stability issues occur, they can be resolved with small capacitors or series RC combinations placed on the input, output, or from input to output.

The LT3092 offers all the protection features expected from a high performance product: thermal shutdown, overcurrent protection, reverse-voltage and reversecurrent protection. Because a simple resistor ratio sets the current, a wide variety of techniques can be utilized to adjust the current on the fly. The LT3092 can also be configured as a linear regulator without output capacitors for use in intrinsic safety environments.

∠ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

Figure 2. SET Pin Current vs Temperature

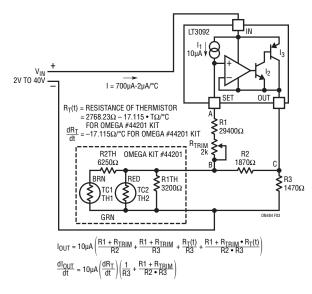

#### The LT3092 as a T-to-I Converter

Omega's 44200 series linear thermistor kits<sup>\*</sup> include thermistors and resistors that together create a linear response to temperature when appropriately configured. These kits generate either a voltage or resistance proportional to temperature with high accuracy; the #44201 kit is listed for the 0°C to 100°C temperature range with 0.15°C accuracy.

Obviously, these kits easily satisfy the needs of a wide variety of applications, but problems arise when the thermistor must be placed at the end of a long wire—application information from Omega suggests no more than 100 feet of #22 wire for thermistor kit #44201. Wire impedance interferes with the thermistor resistance and defeats the accuracy inherent in the kit.

By adding the LT3092 to the thermistor kit along with three 0.1% accuracy resistors and one final trim, a very accurate 2-terminal temperature-to-current converter can be built. This circuit measures 700 $\mu$ A operating current at 0°C, dropping by 2 $\mu$ A every degree until 100°C, at which point the current measures 500 $\mu$ A. The obvious advantage to this T-to-I converter over a T-to-V converter is that current remains constant regardless of the wire length—as long as there is sufficient voltage to meet the compliance of the LT3092 circuit while not exceeding its absolute maximum. Electronics 101: Kirchoff's laws dictate conservation of current in the wire runs as long as there are no nodes for current to leak along the run.

#### Data Sheet Download

www.linear.com

Linear Technology Corporation 1630 McCarthy Blvd., Milpitas, CA 95035-7417 (408) 432-1900 • FAX: (408) 434-0507 • www.linear.com Figure 3 shows the schematic for linear thermistor kit #44201 from Omega with the LT3092 and the additional resistor values. The formulas under the figure allow for substitution of other thermistor kit values and determination of appropriate complementary resistors to fit the application.

Once the initial circuit is built, any initial tolerance, variations, and offsets are easily trimmed out by connecting a voltmeter from node A to node B and trimming the potentiometer to measure 302mV (for this design). This voltage remains constant regardless of temperature.

Now, one wire runs out and back for temperature sensing at significant distances. By providing input voltage above the compliance level of the LT3092 (less than 2V for this circuit and resistor combination) and sensing the resultant current (use a 1k resistor and DVM) one can measure temperature. Figure 4 shows the current output from the circuit across temperature and the difference between measured and calculated response.

#### Conclusion

\*Available from www.omega.com

The LT3092 requires only two external resistors to produce a 2-terminal current source that references to input or ground, or sits in series with signal lines.

A 2-terminal current source enables a number of applications, especially those involving long wire runs, as Kirchoff's laws dictate the conservation of current over long wire distances—distances where a voltage signal would be corrupted. The example presented here uses the LT3092 and a linear thermistor kit to convert temperature to current, creating a 2-terminal current output thermometer. Placing this in series with long distances of wire maintains accuracy despite the distance of wire used.

Figure 4. Calculated vs Measured Performance of the Thermometer in Figure 3.

For applications help, call (408) 432-1900, Ext. 3805

dn484f LT/AP 1110 226K • PRINTED IN THE USA

# **POWER ISLANDS** CUT POWER AND COSTS IN DEEP-SUBMICRON DESIGNS

BY MARTIN ROSICKY AND MARK BARRY • S3 GROUP

oday's imperative to reduce power in both mobile and mains-powered devices is forcing engineers to search for cost-effective ways to reduce power consumption in their designs. Voltage scaling and voltage gating are useful approaches for reducing dynamic and leakage power. Adding power islands to a product may seem like a no-brainer in the race to beat your competitors. However, your decision to do so

may become more difficult if this step adds several years' worth of engineering effort, delays tape-out, and adds to your die's cost.

Although many techniques exist for reducing power consumption, the most common approach for today's deep-submicron designs is to implement power islands. The implementation of power islands yields substantial returns on investment, from reducing packaging and cooling costs to increasing revenues and margins due to longer battery life and longer product lifetime. These considerations have a large impact on your profits.

#### WHY USE POWER ISLANDS?

Increasing levels of integration and the availability of deep-submicron technologies result in opportunities for innovative power management. Power consumption itself is important, particularly in battery-operated devices. However, increasing power density is also important. Pay close attention to this parameter because failure to do so can damage the device or dramatically shorten its lifetime. Power management is a must for most designs implemented in technologies smaller than 90 nm.

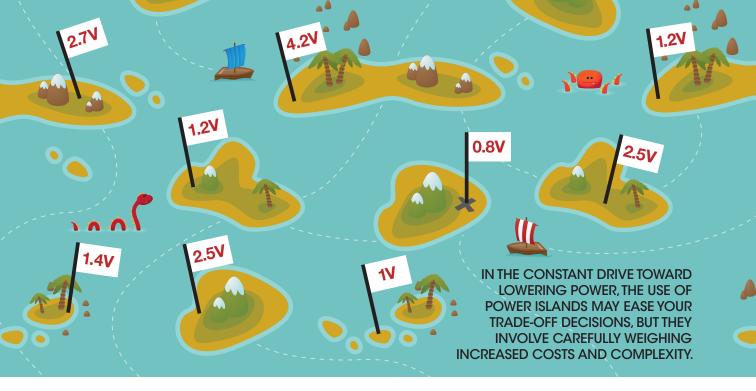

Both static- and dynamic-power consumption are proportional to the power-supply voltage. Power voltage scaling and voltage gating are among the most effective power-saving methods. However, for performance reasons, it is sometimes impossible to reduce voltage for the whole device, and performance requirements of some parts of the design can differ dramatically.

Typically, most of the peripherals can operate at a lower frequency than that of the chip core. The full voltage supply that a high-performance core requires is often unnecessary for its peripheral blocks (**Figure 1**). Moreover, various blocks spend a substantial amount of time in idle mode. Therefore, you can achieve huge power savings by reducing or even switching off power for low-performance and idle blocks. To separately handle the power supply for blocks, you must split the design into power islands. Such intervention requires careful analysis, planning, and implementation, which result in inevitable overhead costs.

#### WHAT IS THE COST?

You must consider many factors when deciding whether to implement power islands. For one thing, they require a more costly architecture and specification phase. Techniques for handling power islands range from the simplest voltage gating of domains to the highest-performance dynamic voltage and frequency scaling. Each technique results in power savings with correspondingly different costs and risks. Your choice of a power-saving

#### AT A GLANCE

Power islands provide opportunities for reducing power consumption but involve increased risks, complexity, and costs.

Using power islands results in a more costly architecture and specification phase and significant NRE (nonrecurring-engineering) cost during implementation.

Consider the impact of power islands on all design tasks.

Minimize the number of power domains and the need for dynamicpower adjustment.

technique depends on your application, the technology, and the risk inherent to power-control implementations. Engineers thus must carefully analyze the design during an architectural study phase to explore these vari-

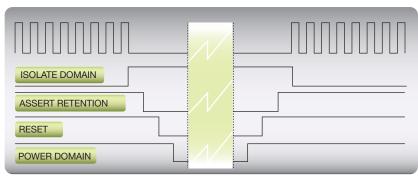

Figure 2 Even the simplest power-down of a domain requires digital control.

ants and propose an optimal design. The output of the study should cover expected power savings and the associated cost and risks. This architectural analysis requires additional NRE (nonrecurring-engineering) costs. It comprises not only the technical staff's effort but often also the EDA-tool-license costs. This support is unavoidable in many cases and may even require expensive ESL (electronic-system-level)tool licenses for architectural exploration. The tools can enable and substantially speed selection of the most effective approach for your design and verify the accuracy and completeness of the power intent. Skimping during this phase or using inappropriate tools can negatively affect NRE costs and risks later in the program.

Splitting your design into power domains yields more modes for functional verification, static-timing analysis, lavout optimization, physical validation, and design for test. This step in itself increases the runtime of all design steps and raises demands on computational power, memory allocation, and data storage. Increasing the number of inputand output-data combinations results in higher demands on data management. Moreover, new tasks appear due to the introduction of power islands. For example, you must design and verify transitions between power modes (Figure 2), including designing and verifying a digital-power-management block that controls power-voltage sources, clock and reset generation, power switches, state retention, and other power structures.

Power-mode-transition sequences can be complex. It is essential to create comprehensive test cases for functional verification and constraints for optimization and timing closure of these various power modes and transitions. Although EDA tools are available to support these tasks, these modes require significant NRE costs for additional RTL (registertransfer-level) design, verification, physical design, and timing closure, including setup of automated flows. Because power modes and sequencing are complex, this step can add risk to the program, compromising core functions and requiring a re-spin.

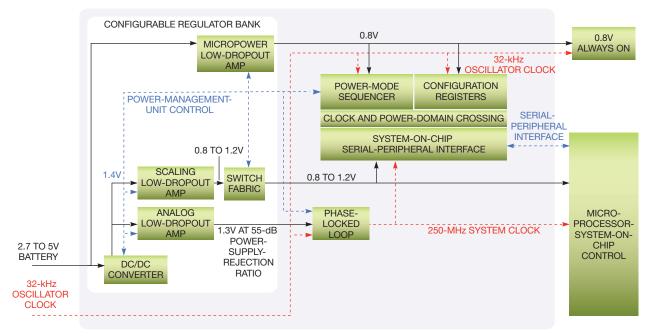

Using power islands can also increase the cost of power-supply generation. Certain power-saving techniques require multiple voltage levels or levels that can

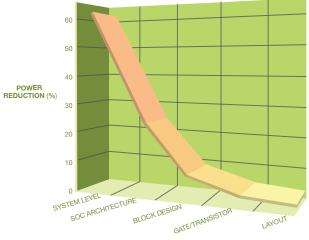

Figure 3 You'll find the largest power reductions early in the design process.

vary with time. The dc/dc converters or linear regulators that supply these additional voltage levels are complex analog blocks. If you intend to integrate these blocks on your IC, consider either the time and effort their design will require or the cost of an IP (intellectual-property) license. The likelihood of purchasing silicon-proven IP exactly matching the needs of your design in the given technology is minimal, and the IP provider typically must customize the IP according to your requirements.

A more complex power source also means an increase in the per-unit cost. For example, a dc/dc converter supplying 400 mA of current may add 7 cents to the die costs in a 65-nm process and potentially push you into a more costly package with more pins to supply the additional 10% or so of current the converter itself loses. Not integrating IP and going instead for an external power-management IC can cost from 1 cent for the addition of a rail to an existing power-management unit to \$1.50 to buy a new dc/dc IC supplying that 400 mA. Additional external components, such as capacitors and inductors, are also necessary, pushing up the BOM (bill-ofmaterials) cost by a couple of cents, adding to OEM-integration NRE costs, and reducing board reliability.

Precision and early power estimation require additional NRE costs. You must base the requirements of the power sources on power-consumption estimates. A power source driving more current than necessary will require more die area and may result in a larger per-unit cost. Too weak a power source is simply a disaster and may result in functional failure. You must consider the additional NRE costs, including EDAtool costs, for the power-consumption estimation in an appropriate design phase. Early estimations are less precise; however. a late start on the power-source design can endanger

the program schedule.

Power-management structures imply area overheads and additional die cost. Digital-power-management blocks inherently require complicated physical power distribution and unavoidable gaps between the power islands. Isolation cells, level shifters, power-management signals, and other structures that relate to the power islands require smaller overheads. They might, however, cause issues in timing-critical or congested designs, increasing the risk to the program schedule.

IP selection is more complicated. You must ensure that you can integrate the IP into your IC using particular low-power techniques. With digital IP, for example, if you wish to use voltage scaling, then it is useful to know at what voltage-frequency pairs in the target technology the IP has been silicon proven. For analog IP, low-power standby modes or full voltage gating may require a redesign. You must pay for any required modification of the IP, increasing risk. Don't underestimate the amount of additional due diligence necessary for IP selection.

Access to voltage-scalable libraries may also increase IP-licensing costs. If your design requires multiple voltage levels, you must have access to more expensive voltage-scalable libraries. Multivoltage support is not yet widespread, however, reducing the number of potential library vendors and, hence, the ability to negotiate on price.

EDA tools supporting power islands

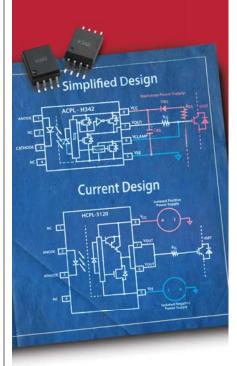

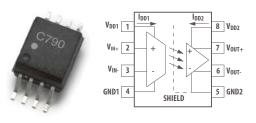

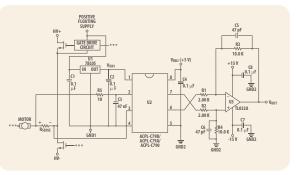

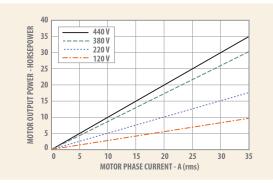

### Simplify Your IGBT Gate Drive Design

Does your next system require a simplified IGBT gate drive design that uses less components and yet not compromise on efficiency and reliability?

If a commitment to excellence and innovative solutions is critical to your design, contact Avago for a free Evaluation Board and Solutions Guide.

four imagination, our innovation

are also more expensive. Implementing power islands requires EDA tools to support simultaneous optimization in MMMCs (multiple modes/multiple corners). EDA licenses enabling these advanced and innovative features are expensive. On the other hand, without the automated-tool support, manual low-power tasks would become difficult, and risks would likely exceed acceptable levels.

You must also consider that EDA tools are still immature, leading to increased risk and increased NRE costs. Despite the fact that the tools have automated many tasks, they are still evolving. You will likely find issues with a tool implementation, and, if you are lucky, you will discover these issues before tape-out. Example issues may include incorrect placement of buffers from one domain within another domain, which could be independently powered off. Another issue arose in which buffers with antenna diodes were placed at the inputs to a power domain. In this case, turning off the power domain caused a large leakage current through the antenna diode from the on domain that was driving it.

In any case, detection of tool issues relies on designers' experience, a deep understanding of the intent, and good luck. It is natural that the tools take some time to mature, but you must consider their imperfections as risks having an impact on effort, time to market, and even the correctness of the design.

Remember that human mistakes and omissions are also likely. Although the EDA tools support system architecture, verification, and implementation, the most important design and data-management tasks require human intervention and experience. Because these issues become more complex when you use power islands, human mistakes and omissions constitute substantial risks.

Using power islands also increases postsilicon validation and productiontest costs. Even after silicon returns, validation of multiple power modes requires increased NRE costs. Production tests may take more time and be more expensive due to the need for multivoltage testing to catch voltage-dependent bridging and delay faults.

Using power islands may incur an additional cost for training of technical staff. To produce competitive results and avoid expensive trial-and-error loops, your engineers may require training in design techniques for voltage islands or use of advanced tool features.

#### **REDUCING OVERHEAD**

Many strategies exist for reducing the overhead you incur when using power islands. First, consider your power strategy upfront. The best chance of

achieving efficient power management for your design is at the architectural stage. Potential power savings dramatically decrease when you postpone decisions to later design phases (Figure 3). Some tools are available for the architectural phase of the design. Using a rough design specification, a list of required IP, technology models, and the like, they can help to partition your design into power domains, select voltage levels, select the most appropriate IP, specify details of the power intent, define functional modes, and select technology. The tools perform rapid what-if analysis and provide early estimations of power, floorplan, package, and die area. Using the results, the tools can then explore the cost benefits of lowpower techniques.

You should consider the impact of power islands on all design tasks. Involve system architects, verification engineers, and implementation engineers in early design planning. Analyze tradeoffs between the power savings and associated verification, implementation, and area overheads as early as possible to build a robust and defensible schedule.

You should also adopt an approach that embraces the main standards for capturing power intent: CPF (Common Power Format) or UPF (Unified Power Format). Using these standards ensures that the power intent remains

Figure 4 ICs with multiple power islands involve complex power-domain management and supply generation.

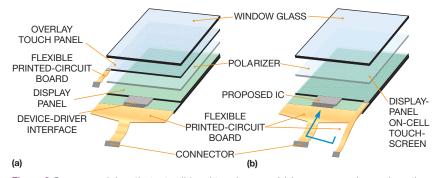

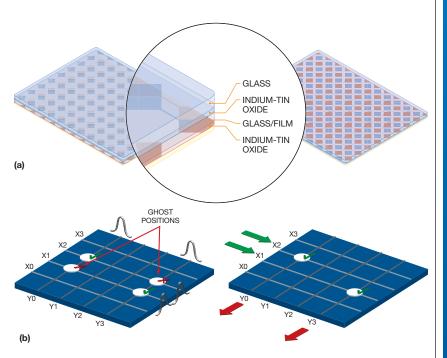

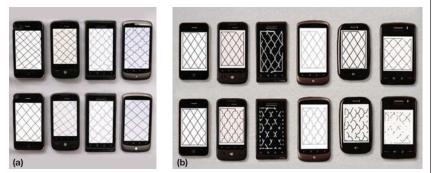

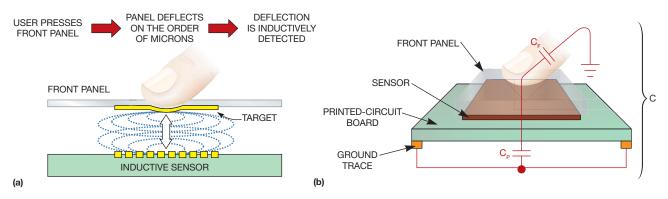

consistent throughout all design steps and is independent of the design data. Advanced EDA tools support CPF/UPF in all design phases. The tools can, for example, emulate and verify the power structures at RTL and their impact on the design's performance without a physical implementation. The tools then automatically insert the power structures into further design steps. CPF and UPF allow power-intent what-if analysis without modifying the verified RTL code. Without the CPF/UPF approach, implementing the power-saving techniques would be more complicated and require additional NRE costs. Hence, a CPF/UPF approach is a must.